Rebellions Unveils Rebel 100 Chiplet Accelerator

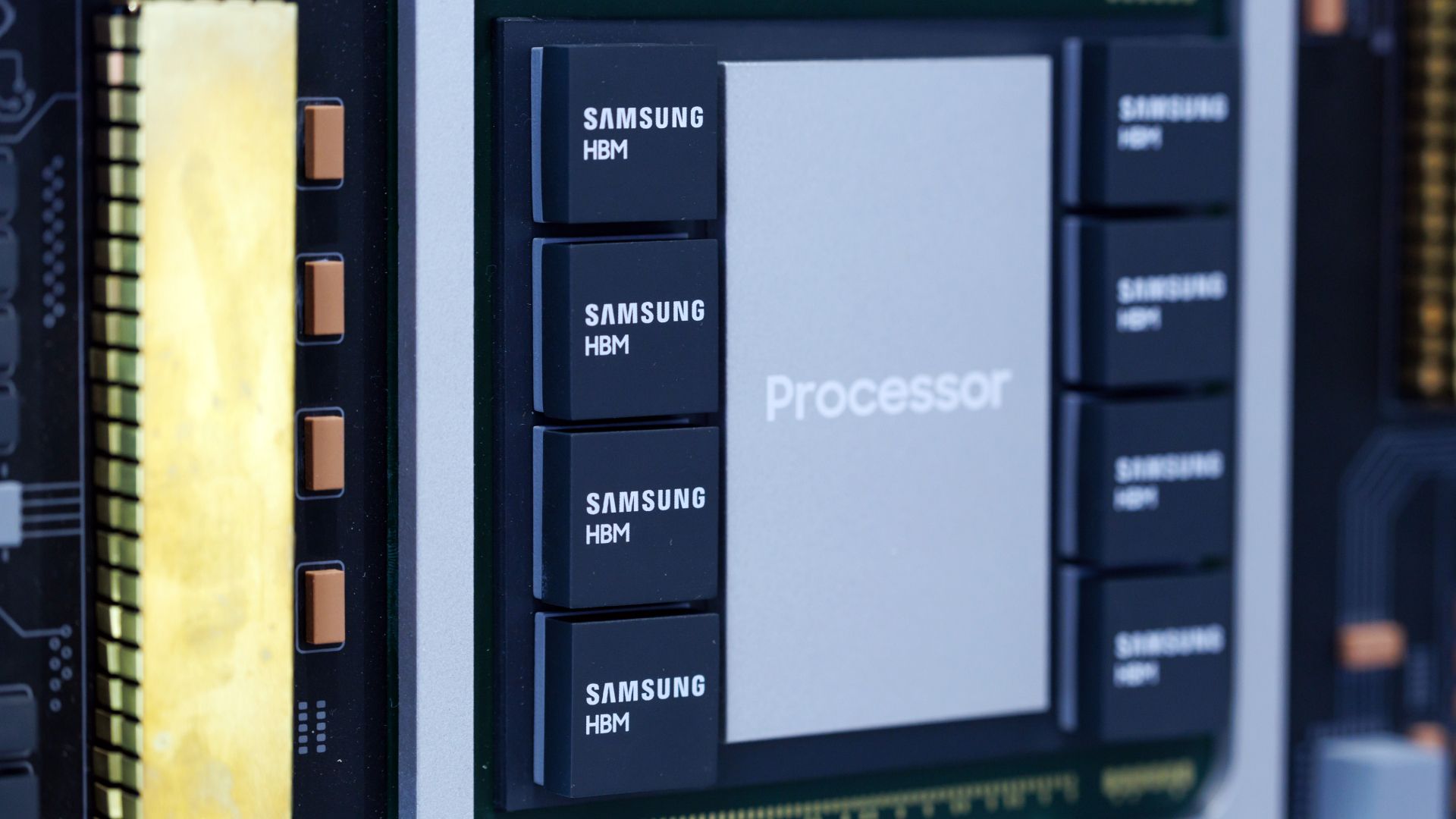

Rebellions detailed its Rebel 100 quad-chiplet AI accelerator at ISSCC 2026, using UCIe-Advanced die-to-die interconnects to stitch four NPUs into a single 2 FP8 PFLOPS (1 FP16 PFLOPS) SiP rated at 600W. Each 320 mm2 NPU die pairs with a 12‑Hi HBM3E 36 GB stack (144 GB per package), a mesh NoC, and aggregated 4 TB/s UCIe bandwidth with ~11 ns FDI latency. The design targets large-model inference scale and rack-level deployment.

Scoring Rationale

Strong technical novelty and broad hardware implications, tempered by vendor-provided performance figures lacking independent verification.

Practice interview problems based on real data

1,500+ SQL & Python problems across 15 industry datasets — the exact type of data you work with.

Try 250 free problems